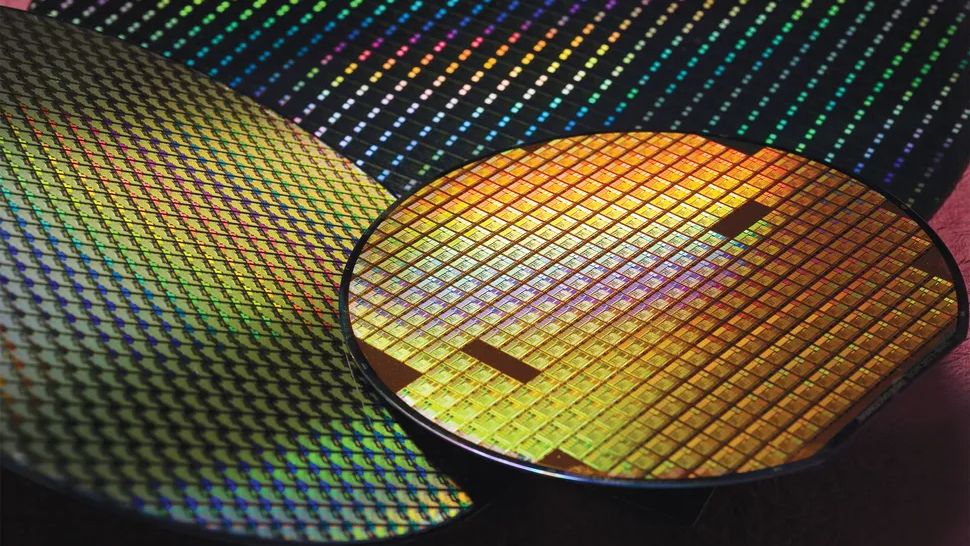

The notion of “a trillion transistors” may sound extravagant, yet it is rapidly becoming a reality. The process of designing cutting-edge transistors today is akin to continually expanding an ever-growing structure. As chiplets are integrated and packaging ascends vertically, elements such as power delivery and interconnects are constantly re-routed to accommodate shifting footprints. Ultimately, the challenge lies not just in the design itself, but in orchestrating all the connections involved.

Cadence aims to tackle this coordination challenge with its newly introduced ChipStack AI Super Agent. Announced on February 10, this innovation embeds an AI-driven assistant within Cadence’s electronic design automation suite, designed to help engineers more efficiently design, debug, verify, and finalize sophisticated semiconductor projects.

“We’re easily going to get over a trillion transistors in the package by the end of the decade,” said Cadence Senior Vice President Paul Cunningham during an interview with Bloomberg. “It’s a phenomenal increase in complexity.”

Focus on Packaging

Cunningham’s focus on “in the package” underscores that reaching a trillion transistors involves not just miniaturizing features at advanced nodes, but also integrating multiple dies into cohesive systems through chiplets, 2.3D interposers, and 3D stacking. As architectural aspirations rise, the demand for design orchestration increases correspondingly.

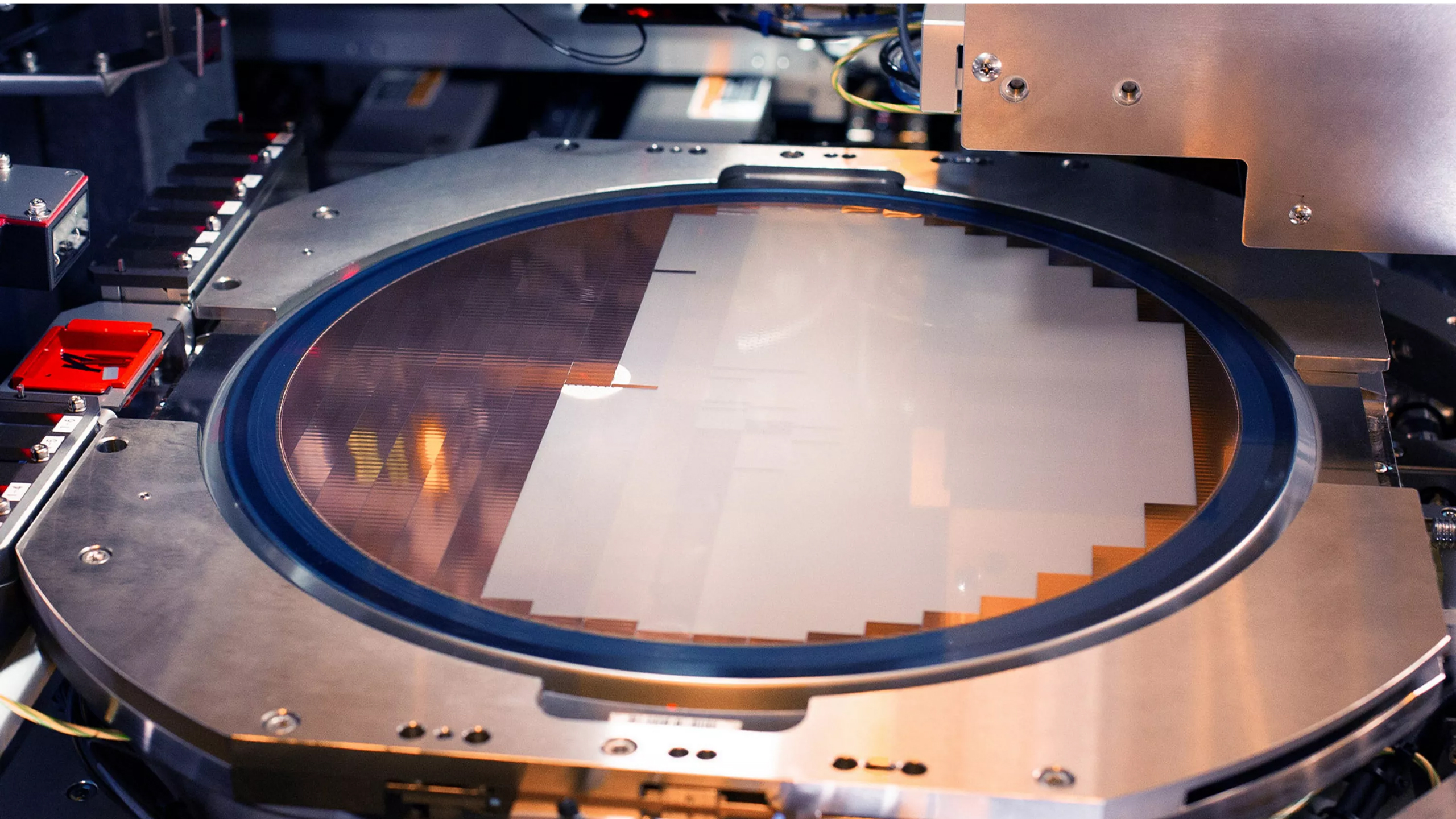

Electronic Design Automation (EDA) has long since automated the intricacies of design, where synthesis, placement, routing, timing analysis, and verification have become deeply algorithmic processes that utilize vast computational resources. Multi-die packages bring additional challenges like interconnect domains, power islands, and require meticulous thermal modeling across stacked silicon. Consequently, verification now extends beyond simple block correctness to include system-level interactions among diverse components.

Engineers navigate these complexities using a combination of layered tool flows, scripts, constraints, and sign-off checks. Reports can become extensive, stretching into thousands of lines, and debugging can take weeks. Cadence’s Super Agent operates above this orchestration layer, functioning as a domain-trained AI that is built on a “mental model” of chip design, as opposed to a generic large language model. This allows engineers to engage with the tool stack conversationally, requesting actions without having to sift through countless scripts or menus.

“You can chat with all of the Cadence products, and they’ll respond,” he mentioned. “You don’t have to be an expert in scripting or learn all the intricate features of our graphical user interfaces. You can simply say, ‘This is what I want to do.’”

Addressing Labor Constraints

The Semiconductor Industry Authority (SIA) anticipates that the U.S. could face a shortage of tens of thousands of skilled workers by the end of the decade. A considerable part of this shortfall is expected to affect engineers and technicians with advanced degrees. While the expansion of fabrication capacity under the CHIPS Act has attracted attention due to workforce shortages, the demand for design expertise is equally pressing.

Advanced-node chip design requires specialists in various fields, including physical implementation, verification methodologies, packaging, signal integrity, and system architecture. These roles necessitate years of specialized training and hands-on experience, but educational institutions are not currently producing graduates at a pace necessary to meet projected demands.

Thus, while the ambition to exceed a trillion transistors is commendable, the requirements for coordination among processes will increase proportionally. More components lead to an uptick in verification scenarios and potential failure modes. Without significant workflow innovations, the design processes will demand increasingly more engineering hours, presenting challenges that may be difficult to meet.

Cadence asserts that the Super Agent can improve productivity by up to tenfold for specific tasks, highlighting its effectiveness in repetitive, report-intensive processes. Nevertheless, even minor reductions in iteration time can significantly impact lengthy design schedules and substantially accelerate development cycles.

Agentic Chip Design

Generative AI has introduced uncertainty across many software domains, prompting questions about whether generalized models could replace specialized tools. EDA vendors operate within a highly regulated environment, dictated by foundry process design kits and sign-off criteria. In this context, tools such as timing analyzers and physical verification cannot easily be substituted by generalized models.

Nonetheless, vulnerabilities exist: for years, working with EDA tools has necessitated a solid grasp of scripting, flow configuration, and the specifics of particular vendor ecosystems. This complexity is partly what has kept customers committed. However, if an external AI assistant could interface with these tools and translate user intent into actionable commands, the barriers could start to diminish.

By integrating a domain-trained model within its existing products, Cadence ensures that the conversational interface remains inherent to its platform rather than being a separate overlay. This ‘Super Agent’ does not replace essential timing engines or verification tools; rather, it acts as an intermediary between engineers and these tools, interpreting user requests and translating them into validated workflows within the Cadence ecosystem. As designs evolve into chiplets and stacked dies, the constraints will only intensify, making an assistant capable of accurately interpreting designer requests crucial for reducing misconfigurations and shortening debugging periods.

Cadence is not alone in this endeavor. Competitors like Synopsys are also developing similar AI-assisted features throughout their portfolios to streamline coordination efforts. If Cadence manages to implement these advancements effectively, it could transform how teams navigate the complexities highlighted by Cunningham.

A trillion transistors in a single package escalates the number of interfaces, verification requirements, and potential failure modes. More dies demand additional cross-domain timing checks, and more silicon stacks require intensive thermal modeling. As previously noted, the coordination load rises correspondingly. If the supply of advanced engineers does not keep pace with demand, the increased burden of coordination must be managed elsewhere. Either development cycles will extend, or the effective output per engineer must rise. Cadence’s initiative strives to achieve the latter within its toolchain.